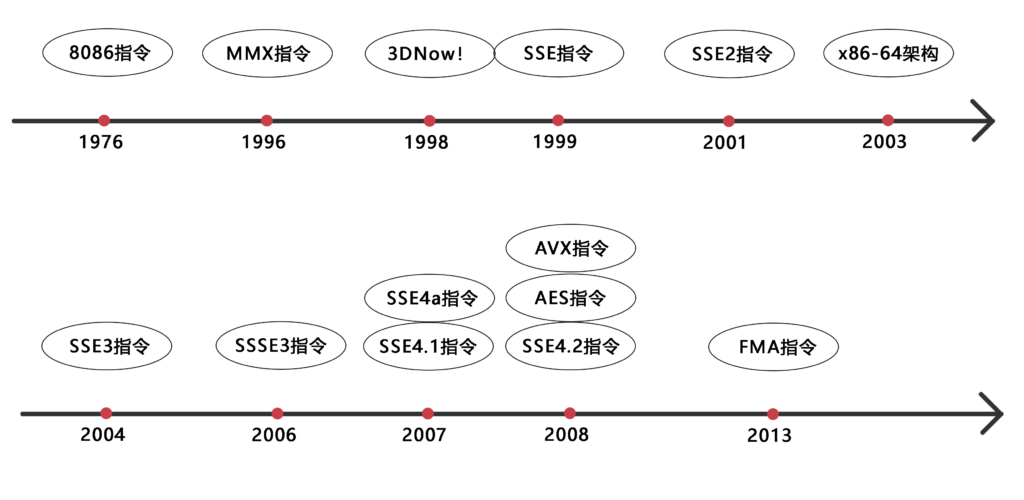

x86 CPU 的发展历程如下图所示:

8086 指令:这个时期的CPU除了有通用寄存器外,还有一个 x87 FPU 单元,用来处理浮点数的。

MMX指令:这是第一个 SIMD 技术,全称是 Single Instruction Multiple Data,也就是一条指令操作多个数据,例如 paddb 指令,可以同时对 八个 8位的整形做加法运算,paddb 指令 的 p 是指 packet ,add 是加的意思,后面的 b 是 byte 字节的意思。这个技术的出现标志着 CPU 进入 Date-Level Parallelism 时代,也就是数据并行处理时代。MMX 使用的寄存器跟 x87 FPU 的寄存器是相同的,所以执行完 MMX 汇编指令 之后切换到 x87 FPU 指令 需要做一些状态处理。

SSE指令:全称 Streaming SIMD Extensions,为什么叫流式我也不太清楚,这个指令集提供了 跟 MMX 一样的多数据处理能力,也可以处理浮点数, 同时带来了 八个 128位的寄存器 XMM0 ~ XMM7,以前 MMX 只有64的寄存器。所以现代汇编应用,普遍会使用 SSE 指令集来替换 MMX 跟 X87FPU,不过CPU需要向后兼容,后面出的新型CPU 还是有 MMX 跟x87 FPU的。MMX 跟 SSE 指令集,有部分指令是重合的。MMX 的指令可以使用 SSE 的寄存器 XMM0~XMM7。

SSE 除了有更大的寄存器,能处理整形,也能处理浮点型。除开这些功能之外,SSE 还有一个更重要的功能,就是扩展了数学表达的能力。提供了求最大,最小,平均值的指令。

举个例子,以前求平均的汇编代码(AT&T风格)如下:

add %ebx,%eax

div $2,%eax上面求平均值需要两条指令,但是用SSE的 pavgb 只需1个指令,还可以操作多个数据,同时求平均值。

pavgb %mm1,%mm2原来你要自己把两个数相加除以2 求平均,现在直接能用一个简单的语法求平均,所SSE扩展的是他的数学表达能力。

3DNow!指令:这个是 AMD 出的指令集,已经过时了,本来是想跟 SSE 竞争的。

SSE2指令:具体可以查看 intel 或者 AMD 的手册,应该是加了一些新的指令。

x86-64架构:这个架构的出现是一个里程碑,标志着计算机系统从 32 位进化到 64位,这里指的是通用寄存器,eax 变成了 rax,支持的内存也从 4GB 上升到 128GB。这个架构的统一经历了很多斗争,在这个过程中,AMD 把自己的x86-64技术叫 AMD64,intel 把自己的x86-64技术 叫 IA-32e 或者 EM64T。不过最后这些东西都统一成 intel64,都叫 intel64。

SSE3指令:具体可以查看 intel 或者 AMD 的手册,应该是加了一些新的指令。

SSSE3指令:新增了16条指令。

SSE4.1指令:这个指令集一共 47 条指令。比较重要的是 提供 点积 的汇编指令,还有crc32 指令,这个函数上层应用经常使用,加密,tcp 都有用。

SSE4a指令:这个指令集一共 4条指令。

SSE4a指令:新增 4条指令。

SSE4.2指令:新增 7条指令。

CPU 一开始只有 加减乘除 + 条件控制 的指令,所有上层应用都能基于这个基石开发出来,无论是操作系统,编译器,图像系统,还是更上层的订单系统,CRM系统,进销存系统等等,这些系统的底层都是一条条 加减乘除指令 + 条件控制 指令 堆叠出来的。

所以CPU指令集历史,现在,未来的发展。主要有两点

1,扩展更多的数学表达的能力。(例如视频标准里面使用到的数学公式,这些标准,必须有芯片行业跟进才能提高计算能力)

2,针对特定的算法提供加速的汇编指令,例如 CRC32。

3,摩尔定律,在集成电路上加更多的晶体管,加快单条指令的执行速度。

扩展知识

1,MMX时代 ,MM0~MM7 已经是 64位的寄存器了 ,为什么这个还是叫32位架构?只有通用寄存器 是64位才能算上是 64位的架构。例如RAX 是64位,这才是 64位架构,EAX 是32位,所以是32位架构,这个指的是通用寄存器。

相关阅读:

由于笔者的水平有限, 加之编写的同时还要参与开发工作,文中难免会出现一些错误或者不准确的地方,恳请读者批评指正。如果读者有任何宝贵意见,可以加我微信 Loken1,QQ:2338195090。